Was wir aus einem viralen Antennen-Post über gutes Prototyping lernen können

Ein unscheinbares Foto einer Testplatine hat auf LinkedIn in kurzer Zeit genau das ausgelöst, was gute technische Inhalte oft auszeichnen: Aufmerksamkeit, Widerspruch und eine lehrreiche Debatte zum IoT-Protyping. Wer in der Hardwareentwicklung schnell lernen will, sollte mehrere Ideen parallel testen, statt auf aufeinanderfolgende Prototypenrunden zu warten. Doch besonders beim Antennendesign kann das problematisch werden.

Zusammenfassung

- Paralleles Prototyping kann in der Hardwareentwicklung helfen, mehrere Designansätze in kurzer Zeit gegeneinander zu testen und Entwicklungszyklen zu verkürzen.

- Im Antennendesign sind Testaufbauten besonders sensibel, weil Antennengeometrie, Groundplane, Bauteilanordnung und Umgebung das Ergebnis direkt beeinflussen.

- Für belastbare Aussagen muss klar zwischen frühem Funktionsscreening und einer echten RF- beziehungsweise Antennenbewertung unter realistischen Bedingungen unterschieden werden.

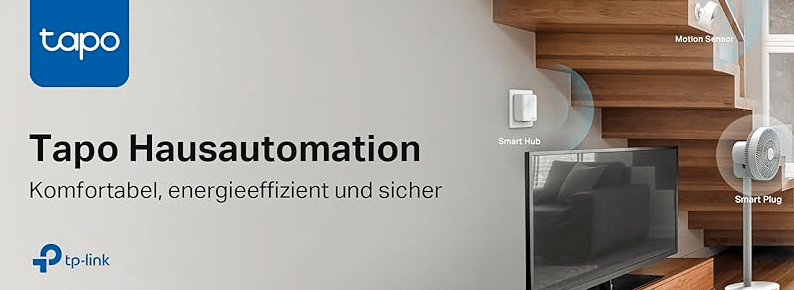

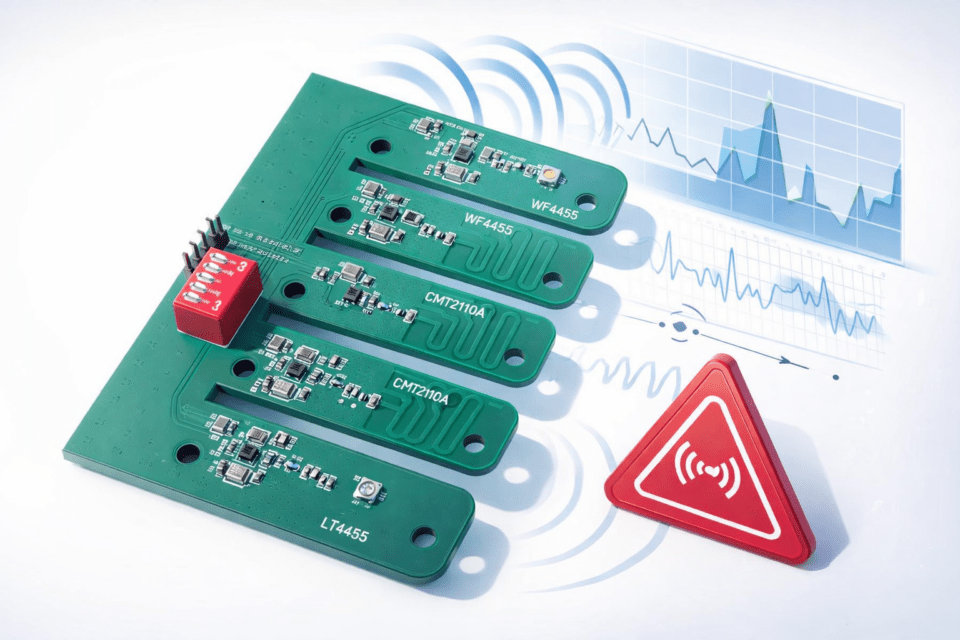

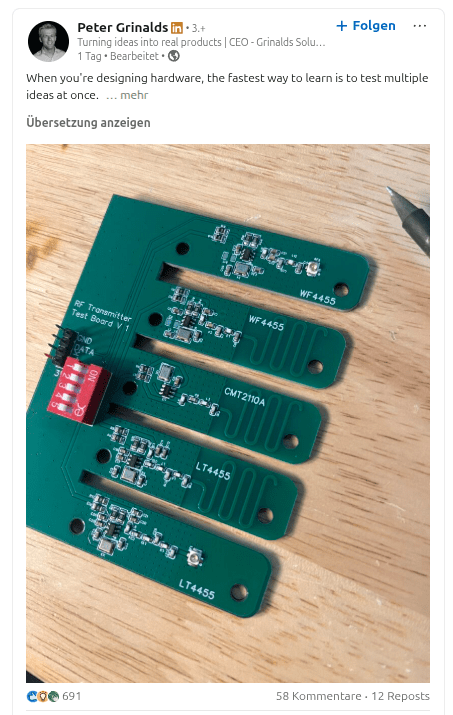

Gepostet hatte das Bild Peter Grinalds, CEO von Grinalds Solutions aus Ohio, USA. Zu sehen: ein RF-Transmitter-Testboard mit verschiedenen Antennen- und Chip-Varianten auf einer einzigen Platine. Grinalds erläuterte, dass es in diesem konkreten Projekt nicht um Strahlungscharakteristik oder finale HF-Performance gegangen sei. Stattdessen habe sein Team in einer frühen Projektphase verschiedene Kombinationen aus RF-Transmitter-Chips, Antennengeometrien und Matching-Netzwerken schnell gegeneinander testen wollen. Das Foto zeigt dabei fünf PCB-Abschnitte: zwei mit dem WF4455, einen mit dem CMT2110A und zwei mit dem LT4455 – jeweils kombiniert mit unterschiedlichen Antennengeometrien. Ein Board, mehrere parallele Experimente, weniger Zeitverlust, geringere Kosten, schnellere Entscheidungen.

Screenshot des LinkedIn-Posts von Peter Grinalds: Das RF-Testboard mit mehreren Antennen- und Chip-Varianten löste eine intensive Debatte über schnelles Prototyping, methodische Grenzen und die Fallstricke im Antennendesign aus.

Als Prinzip für frühes Prototyping ist das nachvollziehbar. Doch das Foto erzählte für viele Fachleute eine andere Geschichte.

Kritik von den Experten

In den Kommentaren meldeten sich zahlreiche Antennen- und RF-Ingenieure zu Wort. Die Stimmung war dabei keineswegs geteilt: Während Generalistinnen und Generalisten sowie Kommentatoren aus dem Fertigungsumfeld den Ansatz grundsätzlich lobten, übte die RF-Fachcommunity nahezu geschlossen Kritik.

Besonders präzise fiel die Analyse von Harald Naumann aus, Gewinner des 5G NTN Antenna Award, und damit eine fachlich gewichtige Stimmen im Thread. Er identifizierte mehrere konkrete Fehler im Aufbau:

- Erstens beeinflussen sich die nebeneinander platzierten Antennen gegenseitig ähnlich wie Lautsprecher, die zu nah beieinander stehen und sich gegenseitig akustisch stören. Der Abstand unterschreitet den für HF-Technik kritischen Mindestwert von Lambda/4 (einem Viertel der Wellenlänge), und alle Antennen sind in dieselbe Richtung ausgerichtet. Das Ergebnis: Jede Antenne „sieht“ nicht mehr ihre eigene Umgebung, sondern eine durch die Nachbarn verfälschte. Katerina G., Senior Antenna Engineer aus Schweden, brachte es im Kommentar auf den Punkt: Das Board verhalte sich damit wie ein Antennen-Array – also ein System aus mehreren absichtlich zusammenwirkenden Antennen – und nicht wie unabhängige Testkandidaten.

- Zweitens beurteilt Naumann die Antennengeometrie kritisch: Die Strukturen seien als L-Antennen ausgeführt, obwohl F-Antennen die bessere Wahl wären. Der Unterschied liegt vereinfacht gesagt im Speisepunkt – also dort, wo das Signal in die Antenne eingespeist wird. F-Antennen bieten dort von Haus aus einen Widerstand von 50 Ohm, was dem Standard der meisten RF-Chips entspricht. L-Antennen tun das nicht, was die Impedanzanpassung erschwert und die Messergebnisse verzerrt.

- Drittens arbeiten die getesteten ICs in unterschiedlichen Frequenzbereichen. Da die optimale Antennenlänge direkt von der Frequenz abhängt – je tiefer die Frequenz, desto länger muss die Antenne sein – passen dieselben Antennenstrukturen schlicht nicht gleich gut zu allen Chips. Ein fairer Vergleich wird dadurch von vornherein erschwert.

- Viertens ist die Groundplane im Testaufbau schlicht zu klein. Gerade PCB-Spurantennen sind hochgradig sensitiv gegenüber der Größe und Geometrie der Massefläche, also der Kupferfläche auf der Platine, die als Gegengewicht zur Antenne wirkt und deren elektrisches Verhalten maßgeblich mitbestimmt. Eine zu kleine Groundplane verändert die Eingangsimpedanz der Antenne massiv, mit einem direkten Folgeeffekt: dem sogenannten „Hand-Effekt“, also einer extremen Empfindlichkeit gegenüber dem Einfluss des Nutzers oder der Umgebung im Betrieb.

Eine Antenne ist mehr als ihr Leiterbahnmuster

Damit ist der eigentliche Kern des Problems benannt. Bei PCB-Antennen ist nicht nur die sichtbare Leiterbahn entscheidend. Auch die Massefläche der Platine, die Position auf dem Board, benachbarte Strukturen und später sogar das Gehäuse sind integraler Bestandteil des Gesamtsystems.

Wer verschiedene Antennenvarianten auf einer gemeinsamen Testplatine nebeneinander platziert, verändert bereits die Bedingungen, unter denen diese Antennen arbeiten. Wird anschließend eine der Varianten allein auf ein separates Board oder ins Zielgehäuse übertragen, ist das elektrisch betrachtet nicht mehr dieselbe Situation. Yury Ilin, Senior Embedded Hardware Design Engineer aus Kanada, machte im Thread einen besonders ernüchternden Punkt: Selbst ein Wechsel des PCB-Herstellers verändert durch abweichende Materialeigenschaften das Antennenverhalten – von VNA-Tuning und Gehäuseintegration ganz zu schweigen.

Was die Community vorschlug: Trennbare Boards als Kompromiss

Mehrere Ingenieure schlugen einen pragmatischeren Mittelweg vor: die Varianten per Mouse-Bites oder V-Scoring trennbar zu gestalten. So können einzelne Abschnitte nach einem ersten Überblick abgebrochen und separat unter realistischeren Bedingungen getestet werden – ohne auf eine komplett neue Fertigungsrunde warten zu müssen. Dieser Ansatz hätte zumindest das Kopplungsproblem entschärft und eine sauberere Einzelmessung pro Variante ermöglicht.

Grinalds selbst reagierte sachlich. Das Board sei nie für eine saubere Antennencharakterisierung gedacht gewesen, sondern nur für eine frühe Vorauswahl zwischen Chipsets und Antennenstilen. Für die eigentliche RF-Bewertung sei anschließend eine dedizierte Platine im Zielgehäuse mit VNA-Abgleich gebaut worden.

Der eigentliche Wert der Debatte: Tempo gegen Genauigkeit

Genau darin liegt der Wert dieser Diskussion – und er geht weit über einen einzelnen LinkedIn-Post hinaus. Der Beitrag von Grinalds war nicht deshalb interessant, weil dort alles richtig gemacht wurde. Er war interessant, weil er einen echten Zielkonflikt in der Hardwareentwicklung sichtbar machte: Tempo gegen Genauigkeit.

In frühen Entwicklungsphasen ist es legitim, Hypothesen schnell auszusortieren. Aber je näher ein Prototyp an physikalisch sensiblen Bereichen wie Funk, Antennen oder EMV arbeitet, desto größer wird das Risiko, dass der Testaufbau die Ergebnisse selbst verfälscht – und damit falsche Sicherheit erzeugt.

Was IoT-Entwickler daraus mitnehmen können

Für die Praxis lässt sich mehr mitnehmen als nur ein viraler LinkedIn-Moment. Ein Prototyp muss auf eine klar definierte Frage antworten – und der Testaufbau darf die Antwort nicht bereits vorwegnehmen oder verzerren. Das gilt besonders im Antennendesign, wo nicht allein die Leiterbahn über den Erfolg entscheidet, sondern das Zusammenspiel aus Geometrie, Antennentyp, Impedanzanpassung, Groundplane-Größe, Gehäuse und realer Einbauumgebung.

Gutes Prototyping maximiert Lernen. Aber nur dann, wenn sauber zwischen funktionalem Screening und echter Performance-Bewertung unterschieden wird. Wer das vermischt, absichtlich oder aus Zeitdruck, riskiert, schnell in die falsche Richtung zu iterieren.

Die eigentliche Lehre aus diesem Post lautet deshalb nicht, dass paralleles Prototyping falsch wäre. Im Gegenteil: Es ist oft klug. Aber bei RF und Antennen gilt mehr als in vielen anderen Disziplinen. Ein schneller Aufbau spart nur dann wirklich Zeit, wenn er nicht zur schnellen Selbsttäuschung wird.